# NOISE TEMPERATURE ESTIMATES FOR A NEXT GENERATION VERY LARGE MICROWAVE ARRAY

Sander Weinreb

Dept. of Physics and Astronomy

U. of Massachusetts

Amherst, MA, 01003

## ABSTRACT

This paper estimates the noise temperature as a function of frequency for amplifiers covering the 1 to 10 GHz range utilizing state-of-the-art HEMT transistors operating at temperatures of 300K, 80K, and 20K. The analysis includes the effect of loss and bandwidth of the input matching network.

## INTRODUCTION

At present the microwave antenna with the largest collecting area on earth is the Arecibo, Puerto Rico 305m diameter spherical reflector with an effective area of approximately 40,000 m<sup>2</sup>. (The Very Large Array, VLA, in New Mexico has an effective area of approximately 10,000 m<sup>2</sup>.) A larger collecting area would greatly increase the sensitivity of the search for extraterrestrial intelligence (SETI), for various radio astronomical observations, and for wide-bandwidth communications with deep-space probes. Initial investigations have started concerning the conceptual design of an antenna with of the order of 10<sup>6</sup> m<sup>2</sup>. A wide variety of formats, ranging from 10 Arecibo-type antennas to 10<sup>6</sup> very small fixed antennas are being considered. In the middle of this range is an array of the order of 10,000 antennas of 9 meter diameter. This latter approach can exploit the technology and cost basis of highly-developed and low-cost direct broadcast satellite receiving systems. The frequency range being considered for this array is continuous coverage of 0.3 to 10 GHz. The purpose of this paper is to estimate the noise temperature and bandwidth of low-noise

amplifiers using current state-of-the-art low noise HEMT transistors operating at temperatures of 300K, 80K, and 20K. This information, together with cost estimates of the receivers, is required to minimize the total cost for antennas, receivers, and processing equipment for a given figure of merit such as effective area or gain divided by system temperature, G/T<sub>sys</sub>.

## METHODOLOGY AND ASSUMPTIONS

Fortunately, the noise-theory and device data needed to solve this problem are well in hand. The field-effect transistor model published by Pospieszalski [1] gives the dependence of noise temperature as a function of physical temperature, frequency, and generator impedance given the equivalent circuit of the transistor as determined by measurements of S-parameters. The transistor noise is described by assigning thermal noise at ambient temperature to all resistors in the transistor equivalent circuit except the drain to source resistance, R<sub>ds</sub>, which is assigned a measured noise temperature, T<sub>drain</sub>. The transistor model for several GaAs and InP HEMT transistors with different width and manufacture (Lockheed-Martin, TRW, and Hughes) have been measured at U. of Massachusetts. The differences between the best transistors of the manufacturers are relatively small and the temperature dependence of the model is also small as observed from the small changes in frequency dependence of several MMIC LNA's that have been cooled from 300K to 20K.

At frequencies below 10 GHz the gate leakage current of InP HEMT's can contribute significantly to the noise temperature. As suggested in [2] the noise due to gate leakage current can be modeled by two shot-noise current sources across the gate- to-source and gate-to-drain junctions of the transistor using the relation,  $i_n^2 = 2 e | I |$ , for each noise generator where  $e = 1.6E-19$ , and  $I$  is the DC  $I_{gs}$  or  $I_{gd}$  leakage current.  $I_{gs}$  and  $I_{gd}$  must be determined separately by measuring  $I_{gs}+I_{gd}$  as a function of  $V_g$  with  $V_d=0$  and  $I_{gd}$  as a function of  $V_d$  with  $V_g=0$ . These measurements have been made on a typical InP 50  $\mu$ m HEMT with the result that  $I_{gs}$  and  $I_{gd} = 2.5$  and  $-2.0 \mu$ A at 300K, .032 and -.030  $\mu$ A at 80K, and .0001 and -.006  $\mu$ A at 20K, all evaluated at the low noise bias point of  $V_g = +0.1V$  and  $V_d = +0.6V$ . These values would increase the minimum noise temperature at 300K by 27K at 1 GHz and 14K at 10GHz; the increase at cryogenic temperatures is negligible. In conclusion, unless gate leakage is reduced the noise of InP transistors will be higher at 300K than GaAs PHEMT's which normally have much lower leakage. A model of a GaAs PHEMT (Kukje KH1032) will be thus be used to predict 300K noise performance and the InP models will be used at 80K and 20K.

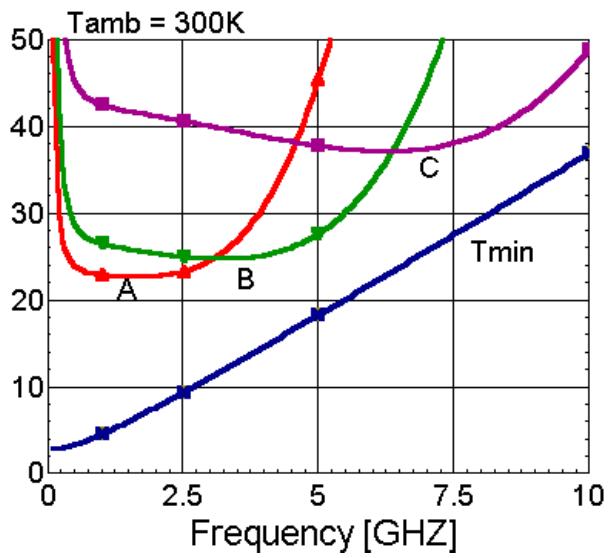

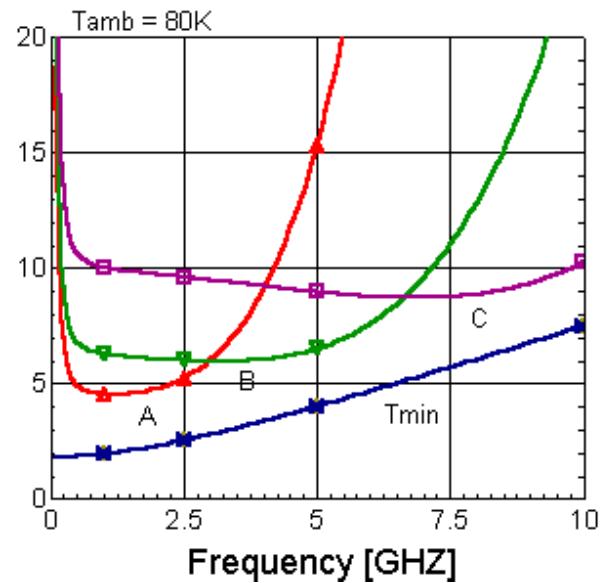

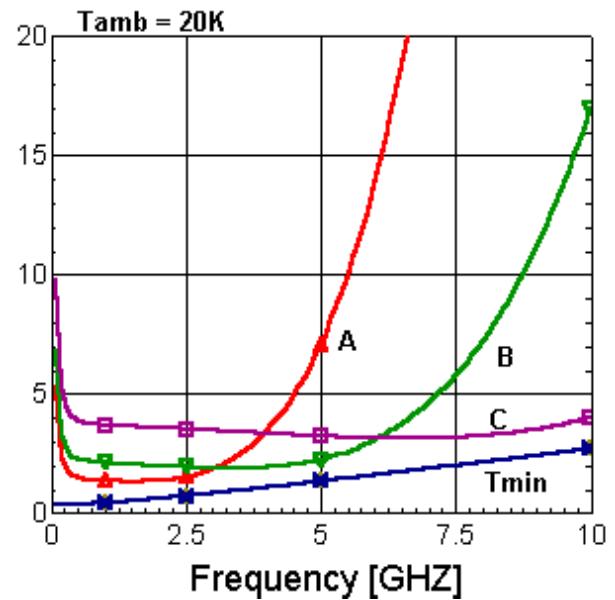

A typical model for a state-of-the-art generic 0.1  $\mu$ m InP HEMT with width 50\*M1 microns is described in Figure 1. The drain noise temperature is a function of temperature and can be determined by one noise figure measurement of the transistor at any frequency. Based upon previously published noise figures such as reported in [3], the cryogenic results reported in [2], and our own measurements of the noise of W-band InP MMIC LNA's, a value of  $T_{drain} = 300K + 6*T_{amb}$  has been used in our analysis, where  $T_{amb}$  is the ambient temperature. This information is sufficient to determine the minimum possible noise temperature,  $T_{min}$ , of the transistor given an ideal, lossless, input matching network.  $T_{min}$  is plotted as a function of frequency at  $T_{amb} = 300K$ , 80K,

and 20K in Figures 3, 4, and 5 respectively.

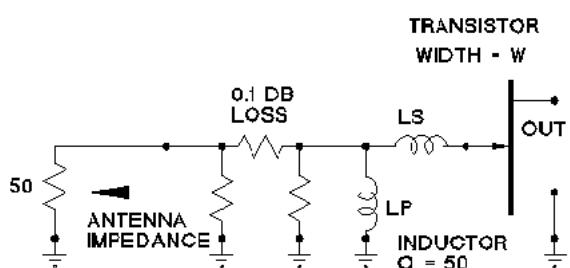

The remaining problem is to determine the noise introduced by a real, lossy, input network and additional transistor noise that occurs because the input matching network cannot produce the minimum-noise generator impedance,  $Z_{opt}$ , over a wide range of frequencies. A simple model of the input matching network, shown in Figure 2, has been selected for this study. The model allows the transistor width to be varied to match the real part of  $Z_{opt}$  to 50 ohms at the middle of the desired frequency range and allows a series inductor,  $L_s$ , to be selected to provide reactance equal to the imaginary part of  $Z_{opt}$  at the center frequency. A shunt inductor,  $L_p$ , is also optimized in the model to attempt to reduce the noise temperature variation with frequency. A Q of 50 is assigned to both inductors as an estimate of the loss of small inductors in this frequency range and a loss of 0.1 dB is added to the input of the amplifier to account for losses in the transmission line and connector or transition to waveguide. An off-chip series inductor may be desirable to achieve high Q. A more complex network with multiple poles could reduce the frequency variation of noise temperature in a specified band but would have more loss and is not considered in this paper. Only the first stage of the low noise amplifier is considered because in the frequency range under 10 GHz the transistor has gain  $> 10$  dB and the second stage will add  $< 10\%$  to the first stage noise temperature.

## RESULTS

The parameters,  $L_s$ ,  $L_p$ , and  $M$  (transistor width) were varied while observing the noise temperature,  $T_n$ , of the amplifier as a function of frequency as computed by the MMICAD circuit simulation program. Gate leakage current was scaled with width. The shunt inductor,  $L_p$ , had little beneficial effect above 1 GHz and a value of 100 nH was used for all cases. Three sets of series inductance and the transistor width were

chosen to minimize the noise temperature in the 1 to 2.5, 2.5 to 5, and 5 to 10 GHz ranges with results shown in Figures 3, 4, and 5 at respective ambient temperatures of 300K, 80K, and 20K. The optimum widths, such as 1500 um for the 1 to 2.5 GHz band, are larger than usually used for low-noise amplifiers (but certainly manufacturable and used for power applications). Smaller widths could give the same result with an input network which transforms the 50 ohm generator to a higher impedance but this will tend to reduce bandwidth. The results of this simple model indicate that wider transistors should be used for wide bandwidth low-noise amplifiers at the low microwave frequencies.

## SUMMARY AND CONCLUSIONS

The results are summarized in Table 1 which shows both the average amplifier noise temperature,  $T_n$ , from Figures 3, 4, and 5, and a first estimate of the total system noise temperature,  $T_{sys}$ , which adds the noise temperatures due to feed loss, ground pickup from spillover, atmospheric noise, and sky temperature. For the cooled receivers it is assumed that the feed transition is also cooled and less noise is added from this source. The results are shown for octave frequency ranges and also for the full decade, 1 to 10 GHz range. The feed loss and spillover contributions need careful study. Efficient octave-band feeds are not easily designed and an efficient decade band feed may not be feasible.

The results show approximately a factor of 3 reduction in system noise temperature by cooling the low-noise amplifier from 300K to 80K. In quantities of 10,000 If we assume costs of \$300 for 300K receivers and \$3000 for 80K receivers including refrigerator and vacuum dewar, the improvement of  $G/T_{sys}$  costs \$81M for a 10,000 element array with 3 octave-band receivers. This needs to be compared with the cost of increasing the total antenna area by a factor of 3.

**Table 1** - Estimated Receiver and System Noise as a Function of Frequency and Temperature

| Ambient Temp. | 1 - 2.5 GHz $T_n/T_{sys}$ | 2.5 - 5 GHz $T_n/T_{sys}$ | 5 - 10 GHz $T_n/T_{sys}$ |

|---------------|---------------------------|---------------------------|--------------------------|

| 300K          | 23/38 K                   | 25/40 K                   | 45/65 K                  |

|               |                           | 45/65 K                   |                          |

| 80K           | 5/17 K                    | 6/18 K                    | 10/22 K                  |

|               |                           | 10/22 K                   |                          |

| 20K           | 2/14 K                    | 3/15 K                    | 4/16K                    |

|               |                           | 5/17K                     |                          |

## REFERENCES

[1] M. Pospieszalski, "Modeling of Noise Parameters of MESFET's and MODFET's and Their Frequency and Temperature Dependence," 1989 IEEE MTT Trans., vol. MTT-37, pp. 1340-1350.

[2] M. Pospieszalski, "Millimeter-Wave Cryogenically-Coolable Amplifiers Using AlInAs/GaInAs/InP HEMT's," 1993 IEEE MTT-S Digest, pp. 515-518.

[3] P. M. Smith, "Status of InP HEMT Technology for Microwave Receiver Applications," 1996 IEEE-S Digest, pp. 5-8.

```

! DEFINE GENERIC 50*M1 um InP HEMT

! MODEL REF PLANE +/- 30uM FROM CENTER

NCS 2 5 I={0.32*MAG(IGD)*M1} R=1E10

NCS 2 3 I={0.32*MAG(IGS)*M1} R=1E10

IND 12 1 L={6+10/M1} ! LG

CAP 12 0 C=7.5 !CPG

RES 1 2 R={4/M1} ! RG

CAP 2 3 C={48*M1} ! CGS

RES 3 4 R=0 ! RI

RES 4 10 R={7.2/M1} ! RS

IND 10 0 L=3.9 ! LS

CAP 2 5 C={7*M1} ! CFI

CAP 5 4 C={2} ! CDS

RES 5 6 R={10/M1} ! RD

CAP 1 6 C=1 ! CFO

CAP 8 0 C={8+10*M1} !CPD

IND 6 8 L=23 ! LD

VDCS 2 5 3 4 GM={60*M1} TAU=0.15 R1=1E6 R2=1E6 &

F=1E6 A=0

REST 5 4 R={170/M1} T={300+6*TEMP}

DEF2P 12 8 PHEMTGS1 !THE FET MODEL

```

**Figure 1** - Circuit file of transistor equivalent circuit including noise sources of a typical InP 0.1 umHEMTtransistor with width equal to  $50*M1$  um.

**Figure 2** - Circuit model used for estimation of the feasible noise temperature as a function of temperature and frequency. The parameters  $L_s$ ,  $L_p$ , and  $W$  were adjusted at each temperature to provide a minimum average noise over the desired frequency range.

**Figure 3** - Noise temperature,  $T_n$ , for 3 designs of GaAs PHEMT amplifiers operating at 300K with the model of Figure 2 optimized for the frequency ranges A (1 to 2.5 GHz), B (2.5 to 5 GHz), and C (5 to 10 GHz). The optimum circuit parameters for the three ranges are (transistor width in  $\mu m$ ,  $L_s$  in  $nH$ ): A (1000, 1.5), B (750, 1.2), and C (400, 0.8).  $T_{min}$  is the minimum noise temperature for the transistor with an ideal, lossless input matching network optimized for each frequency.

**Figure 4** - Same as Figure 3 except for InP amplifiers operating at 80K. The optimum circuit parameters (width  $\mu m$ ,  $L_s$   $nH$ ) are: A (1500, 2), B (600, 1.2) and (300, 0.8)

**Figure 5** - Same as Figure 3 except for InP amplifiers operating at 20K. The optimum circuit parameters (width  $\mu m$ ,  $L_s$   $nH$ ) are: A (1250, 2.5), B (600, 1.5), and C (300, 0.8).